[Article ID] 1003- 6326( 2001) 05- 0753- 03

# Characteristics of Si<sup>+</sup> / B<sup>+</sup> dual implanted silicon wafers<sup>0</sup>

ZHOU Jircheng(周继承), HUANG Bairyun(黄伯云) (State Key Laboratory for Powder Metallurgy, Central South University, Changsha 410083, P. R. China)

[Abstract] Thin  $p^+$  layers with good electrical properties were fabricated by RTA (rapid thermal annealing) with post-FA (furance annealing) of Si<sup>+</sup>/B<sup>+</sup> dual implanted silicon wafers. The electrical and structural characteristics of thin  $p^+$  layers have been measured by FPP (four-point probe), SRP (spreading resistance probe), RBS/channelling. Optimizing the implantation and annealing processes, especially using the thermal cycle of RTA followed by FA, shallow  $p^+$  n junctions can be fabricated, which shows excellent FV characteristics with revers-bias leakage current densities of 1.8 nA/cm<sup>2</sup> at  $-1.4\,\mathrm{V}$ .

[ **Key words**] rapid thermal annealing; dual ion implantation; silicon thin p<sup>+</sup> layers [ **CLC number**] TN 304. 055; TN 305. 3 [ **Document code**] **A**

### 1 INTRODUCTION

For silicon-photo-diodes (SPD), it is necessary to form shallow  $p^+$  n junctions with very low reverse-bias leakage current densities. To form thin  $p^+$  layers, both the doping and annealing steps must be optimized. Ion implantation steps must be taken to e-liminate ion channelling<sup>[1]</sup>, either by pre-amorphizing the surface layer<sup>[2,3]</sup> or by using a heavy molecular ion beam such as  $BF_2^+$ ,  $B_{10}H_{14}^{[4,5]}$ . Diffusion can be limited when short annealing time or lower temperature is applied. RTA is very effective for dopant to have high activation and low redistribution<sup>[6~7]</sup>.

This paper shows that thin p<sup>+</sup> layers with excellent electrical properties can be produced by Si<sup>+</sup>/B<sup>+</sup> dual implantation and RTA followed by FA. It just contrasts with Ref. [8], in which the author revealed that only the thermal cycle of FA followed by RTA can fabricate the shallow p<sup>+</sup> n junctions with good characteristics.

#### 2 EXPERIMENTAL

Phosphorus doped (0.8 ~ 1.2  $\Omega^{\bullet}$  cm) CZ m type (100) silicon wafers were used throughout this work. Implantation parameters for p<sup>+</sup> layers were listed in Table 1. Two sets of Si<sup>+</sup> pre-amorphization were employed: the first, thin amorphous layer, i. e. 40 keV Si<sup>+</sup> pre-implantation to a dose of  $3.0 \times 10^{15}$  cm<sup>-2</sup>, producing an amorphous layer about 100 nm thick; the second, thick amorphous layer, i. e.  $80 \, \text{keV Si}^{+}$  pre-implantation to doses of  $1.5 \times 10^{15}$  cm<sup>-2</sup> and  $3.0 \times 10^{15}$  cm<sup>-2</sup>, producing an amorphous layer

about 140 nm and 210 nm thick, respectively. After amorphization of the surface, all the wafers were implanted with 20 keV B<sup>+</sup> to a dose of  $5.0 \times 10^{14}$  cm<sup>-2</sup>. A single implantation control wafer was prepared by an implantation of 20 keV B<sup>+</sup> ions to a dose of  $5.0 \times 10^{14}$  cm<sup>-2</sup>. Implantation was performed at a tilt angle of  $7^{\circ}$  on a water-cooled target. All wafers underwent rapid isochronous annealing at temperatures ranging from 800 °C to 1150 °C for 20s or rapid isothermal annealing at 1100 °C for  $5 \sim 60 \, \text{s}$  in dry  $N_2$  ambient.

The SPD with a junction area of  $2500\,\mu\text{m} \times 3000\,\mu\text{m}$ , with the same RTA conditions and implantation parameters as above studies, was fabricated by a special process. The diodes fabricated with B<sup>+</sup> single implantation were performed to compare with the Si<sup>+</sup>/B<sup>+</sup> dual implantation diodes.

The carrier concentration depth profiles were measured by SRP technique. SRP, in conjunction with FPP measurements of sheet resistance, can also provide information about the degree of dopant activation. The depths of amorphous layers, the crystal quality, and the residual damage were characterized by RBS/ion channelling.

#### 3 RESULTS AND DISCUSSION

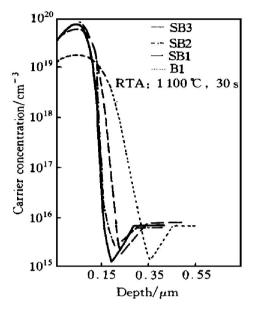

Fig. 1 shows carrier concentration depth profiles. The junction depth  $X_j$  is not greater than 0. 24  $\mu$ m in all cases except for B<sup>+</sup> single implantation, where  $X_j$  = 0. 38  $\mu$ m. For sample No. SB3, after 1 100 °C, 30 s RTA, the junction depth is 0. 18  $\mu$ m and the sheet resistance  $R_s$ = 80  $\Omega$ /  $\square$ . SRP, in conjunction with FPP, also provides that about 97% boron atoms are activated after RTA at 1 100 °C for 30 s, while

① [Foundation item] Project (69971007) supported by the National Natural Science Foundation of China; Project supported by Huo YinDong Foundation; Project supported by EYTP of Ministry of Education, P. R. China

| - |     |                                      | Table 1     | Implantation parameters                   |                                    |

|---|-----|--------------------------------------|-------------|-------------------------------------------|------------------------------------|

|   | No. | Ion                                  | Energy/ keV | Dose/ $cm^{-2}$                           | Dose rate/ $(\mu A \cdot cm^{-2})$ |

|   | B1  | $B^{+}$                              | 20          | $5.0 \times 10^{14}$                      | 0. 19                              |

|   | SB1 | $\mathrm{Si}^+$ / $\mathrm{B}^+$     | 40/20       | $3.0 \times 10^{15} / 5.0 \times 10^{14}$ | 0. 39/ 0. 17                       |

|   | SB2 | $\mathrm{Si}^{+}$ / $\mathrm{B}^{+}$ | 80/20       | $1.5 \times 10^{15} / 5.0 \times 10^{14}$ | 0. 39/ 0. 17                       |

|   | SR3 | S;+ / R+                             | 80/20       | $3.0 \times 10^{15} / 5.0 \times 10^{14}$ | 0.39/0.17                          |

**Fig. 1** Carrier concentration depth profiles after RTA at 1 100 °C for 30 s

the activation degree is only 37% for B<sup>+</sup> single implantation wafer. Therefore the optimization of dual implantation parameters and RTA conditions must be taken to form a thin p<sup>+</sup> layers with good quality.

Because of the high degree of dopant activation, from the carrier concentration depth profiles in Fig. 1, we can also observe the diffusion of boron as functions of annealing time and temperature in crystalline and  $\mathrm{Si}^+$  preamorphized substrates. There is a very fast diffusion in the crystalline wafer (sample No. B1), perhaps due to interstitial processes; but in  $\mathrm{Si}^+/\mathrm{B}^+$  dual implantation wafers, the RTA deeply eliminates the diffusion.

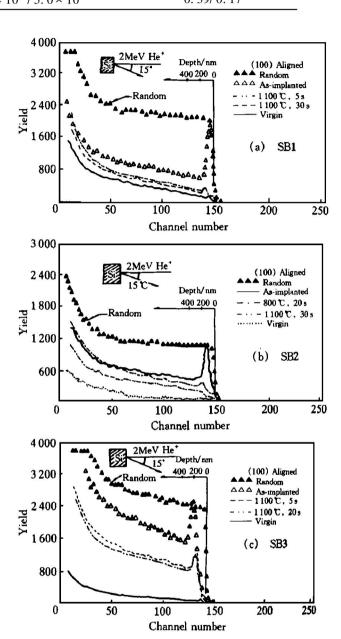

The production of sharp implanted dopant profiles is strongly dependent on the nature of the amorphized region. Ion energy, ion dose, ion species and the substrate temperature are very important variables in the formation of amorphous layers. RBS/ ion channelling spectra (Fig. 2) shows the influence of some of these variables on the amorphization of silicon substrates and annealing. For example, the  $80\,\mathrm{keV}$  Si<sup>+</sup> implantation to a dose of  $1.5\times10^{15}$  cm<sup>-2</sup> at watercooled target temperature yielded an 140 nm thick amorphous layer. For Si<sup>+</sup>/B<sup>+</sup> dual implantation wafers, RBS/ ion channelling data show that an initial damage (amorphous) peak is eliminated while some residual damage still remains after RTA at  $1\,100\,^{\circ}\mathrm{C}$  for  $15\,\mathrm{s}$  or longer. In the same time, we should note

**Fig. 2** (100) aligned RBS channelling spectra for Si<sup>+</sup> / B<sup>+</sup> dual implanted samples

that high dose B<sup>+</sup> single implantation induced damage is much more difficult to anneal out<sup>[6]</sup>.

The effects of the implantation parameters and annealing conditions on the reverse bias leakage current density J are also investigated. Post-FA (800 °C, 20 min) has effectively reduced the reverse bias leakage current. Annealing methods do not affect the bulk component of leakage current, while RTA will increase the surface component. The reason for this phenomenon may be that bulk g-r (generation-

recombination) centers in the Si/SiO2 interface layer near p<sup>+</sup> n junction and/or interface state densities will increase after RTA, while post-FA can eliminate them. The leakage current density of sample No. SB3 is about 3 orders of magnitude higher than that of sample No. SB1 and possesses the same order of magnitude as that of sample No. SB2. The smallest releakage current density (No. SB1)  $1.8 \, \text{nA/cm}^{-2}$  at  $-1.4 \, \text{V}$ . These results show that Si<sup>+</sup>/B<sup>+</sup> dual implantation parameters must be optimized and Si<sup>+</sup> / B<sup>+</sup> dual implantation and RTA combined with post-FA technique can be applied to fabricate silicon photo diodes with shallow p<sup>+</sup> n junctions, while B<sup>+</sup> single implantation or only FA will induce much deeper junction and greater leakage current.

## 4 CONCLUSIONS

Both RTA and pre-amorphization are required to form thin  $p^+$  layers. The induced damage which was produced by  $Si^+/B^+$  dual implantation can be removed by RTA.  $Si^+$  preamorphization can effectively inhibit the Boron channelling effect. RTA combined with post-FA and  $Si^+/B^+$  dual implantation can be used to fabricate silicomphoto diodes with good electrical characteristics, while  $B^+$  single implantation or  $Si^+/B^+$  dual implantation then only FA will form

much thick p<sup>+</sup> layers.

#### [REFERENCES]

- [1] Hong S N, Ruggles G A, Wortman J J, et al. Material and electrical properties of ultra shallow p<sup>+</sup> n junctions formed by low-energy ion implantation and rapid thermal annealing [J]. IEEE Trans. Electron Devices, 1991, 39: 476.

- [2] Tsien P H, Hou D Y, Lin H W, et al. Rapid thermal processing technology for ULSI [J]. Acta Electronica Sinica, (in Chinese), 1992, 20(11): 1.

- [3] ZHOU J C. Influence of preamorphized implantation on silicon p<sup>+</sup> n junction properties [J]. Functional Materials, (in Chinese), 1999, 30(4): 373.

- [4] Kionshila H, Kwong D L. Physical model of the diffusion of ion implanted boron and BF<sub>2</sub> during rapid thermal annealing [J]. IEDM Tech Dig, 1992, 165.

- [5] Gato K, Matsuo J, Sugii T, et al. Novel shallow junction technology using decaborane (B<sub>10</sub>H<sub>14</sub>) [J]. IEDM Tech Dig, 1996: 435.

- [6] ZHOU J C, JIANG X Y, ZHU J L. Characteristics of silicon thin p<sup>+</sup> layers [J]. Chinese J of Electronics, 1997, 6(4): 10.

- [7] WANG J, TU H L, LIU A S, et al. In situ observation of annealing behavior of hydrogen implanted silicon in high voltage electron microscope [J]. The Chinese Journal Nonferrous Metals, 1998, 8(4): 626.

- [8] Hong S N. 0. 2 \( \mu\) m p<sup>+</sup> n junction characteristics dependent on implantation and annealing processes [J]. IEEE Electron Device Lett, 1999, 20(2): 83.

(Edited by HE Xue-feng)